# Features

- Operating voltage 3.0-5.5V

- Built-in RC oscillator

- Max. 12 SEG and 8 GRID(Number of SEG pins in different packages)

- SEG pins connect to LED Anode, GRID pins connect to LED Cathode

- I2C bus interface,I2C slave address can be configured through IO pins

- 16-level brightness control

- Max. 10 × 3 key scan Key display multiplexing requires hardware circuit Supporting combination keys requires circuit

- Read/Write address auto increment

- Dispaly mode 12x8

- Power-On Reset(POR)

- Versatile blinking modes

- Standby mode

- High driving current, suitable for highlighted applications

- Package: SOP24(300mil)(15.40mm x 7.50mm PP=1.27mm) ·

# **1** General Description

The VK16K33B is a memory mapping and multi-function LED controller driver. The max. Display

segment numbers in the device is 96 patterns (12 SEG x 8 GRID) with a  $10 \times 3$  (MAX.) matrix key scan circuit. The software configuration features of the VK16K33B makes it suitable for multiple LED

applications including LED modules and display subsystems. The device communicates with host microcontrollers via a two-line bidirectional I2C bus, it is used to configure display parameters and transfer display data, and can also enter the standby mode through System Set Command .

2/21

# 2 Pinouts and pin description

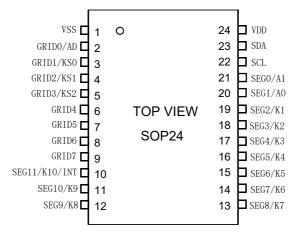

#### 2.1 VK16K33BSOP24 Pin Assignment

VK16K33B 12×8 LED DRIVER

# 2.2 VK16K33B SOP24Pin Description

| No.   | Name                    | I/O | Function                                                                                                                                                                                                                                                                                                                                                                                                         |

|-------|-------------------------|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1     | VSS                     | VSS | Negative power supply                                                                                                                                                                                                                                                                                                                                                                                            |

| 2     | GRID0/AD                | 0   | LED GRID outputs (N-MOS open drain)<br>I2C slave address source output pin, active high during power on and key scan <b>*1</b>                                                                                                                                                                                                                                                                                   |

| 3-5   | GRID1/KS0-<br>GRID3/KS2 | 0   | LED GRID outputs(N-MOS open drain );<br>Key source output pin, active high during key scan operation                                                                                                                                                                                                                                                                                                             |

| 6~9   | GRID4 ~GRID7            | 0   | LED GRID outputs (N-MOS open drain )                                                                                                                                                                                                                                                                                                                                                                             |

| 11-19 | SEG10/K9-<br>SEG2/K1    | I/O | LED SEG outputs (P-MOS open drain) ;<br>Key data input pin, internal pull-low during key scan operation                                                                                                                                                                                                                                                                                                          |

| 20-21 | SEG1/A0-<br>SEG0/A1     | I/O | LED SEG outputs (P-MOS open drain)<br>I2C slave address setting pin, 4 address 0xe0-0xe3 can be set,<br>and bit0 is the read / write bit. <b>*1</b>                                                                                                                                                                                                                                                              |

| 22    | SCL                     | 0   | Serial Clock Input for I2C interface                                                                                                                                                                                                                                                                                                                                                                             |

| 23    | SDA                     | I/O | Serial Data Input/Output for I2C interface                                                                                                                                                                                                                                                                                                                                                                       |

| 24    | VDD                     | VDD | Positive power supply                                                                                                                                                                                                                                                                                                                                                                                            |

| 10    | SEG11/K10<br>/INT       | I/O | <ul> <li>I. when bit0 of SEG / INT register is set to "0", this pin is LED SEG output (P-MOS open drain) and Key data input during key scan operation.</li> <li>II. when bit0 of SEG / INT register is set to "1", this pin is Interrupt signal (INT) output pin bit1 of SEG/INT register is set to "0", INT pin output active-low bit1 of SEG/INT register is set to "1", INT pin output active-high</li> </ul> |

**\*1** I2C slave address is updated during power on reset or key scanning cycle.

# **3** Functional Description

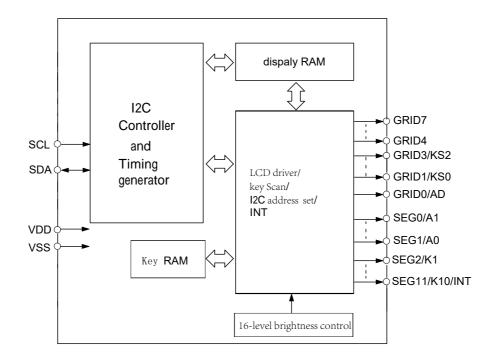

#### 3.1 Block diagram

#### 3.2 Power-On Reset

When the power is applied, the device is initialized by an internal power-on reset circuit. Data transfers on the I2C bus should be avoided for 1 ms following power-on.

The status of the internal circuits after initialization is as follows:

System Oscillator is off state GRID0~GRID3 outputs are set to VDD. **GRID4~GRID7** outputs are set to high impedance. all SEG pins are set to input. LED Display Off. Key scan stopped. SEG/INT pin is set to SEG. brightness is set to 16/16 duty<sub>o</sub>

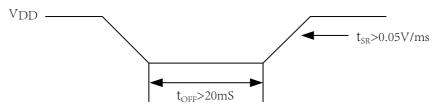

if VDD drops below the minimum voltage of operating voltage specification during operation, the power-on reset timing conditions must be also satisfied. This means that VDD must fall to 0V and remain at 0V for a minimum time of 20ms before rising to the normal operating voltage.

Power-on Reset Timing

### 3.3 Standby Mode & Wake-up

#### Standby Mode

In the standby mode, the VK16K33B can not accept input commands nor write data to the display RAM

except using the system setup command.

If the standby mode is selected with the bit0 of the System Set Command set to  $0^{\circ}$ , the status of the standby model is as follows:

- System Oscillator is off state

- GRID0~GRID3 outputs are set to VDD.

- GRID4~GRID7 outputs are set to high impedance.

- all SEG pins are set to input.

- LED Display Off.

- Key scan stopped.

- All key data and INT flags are cleared until the standby mode is canceled.

- If any key is pressed or the bit0 of the System Set Command is set to "1", the standby mode will be canceled and will cause the device to wake-up.

- If the bit0 of the SEG/INT register is set to  $0^{\circ}$ , all SEG pins are changed to input pins.

- If the bit0 of the SEG/INT register is set to "1" : all SEG pins are changed to input pins except for the INT pin (output).

- ullet The INT pin output remain at a high level when the bit 1 of the SEG/INT register is set to "0".

- ullet The INT pin output remain at a low level when the bit1 of the SEG/INT register is set to "1".

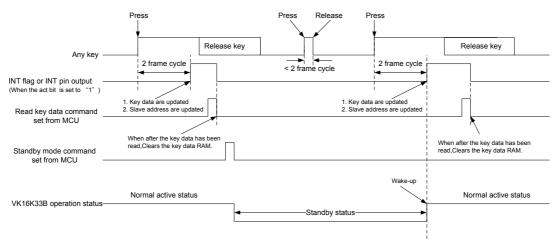

#### Wake-up

- Wake-up by any key or by set the bit0 of the System Set Command to "1". A key scan will then be performed.

- The System Oscillator restarts for normal operation.

- The previous display data output will be updated by Each Mode command set.

The relationship between the Wake-up and any key press is shown as follows:

7/21

# 3.4 Display RAM

The static display memory (RAM) is organized into  $16 \times 8$  bits and stores the displayed data. The contents of the RAM are directly mapped to the contents of the LCD driver. Display address is 0x00-0x0F, the RAM size is 16 bytes. If you want to lighted on or off an LED, only set or clear the corresponding display RAM bit to 1 or 0, For example, if LED1 driven by SEG0 pin and GRID1 pin is on or off, only set bit0 to 1 or 0 of the corresponding display RAM (0x00). The ram bit corresponding to the unused SEG pin is cleared to 0.

The following is a mapping from the RAM to the LED pattern:

| SEG   |    |    |    |    | SE  | SEG | SE | SEG     | Addr | SE | SE | SE      | SE | SE | SE | SEC    | SEG0 | Addr  | SEG   |

|-------|----|----|----|----|-----|-----|----|---------|------|----|----|---------|----|----|----|--------|------|-------|-------|

| GRID  |    |    |    |    | G11 | G10 | G9 | С)<br>8 | Addi | G7 | G6 | ς)<br>Ο | G4 | G3 | G2 | Ω<br>Ω | 0    | riddi | GRID  |

| GRID0 |    |    |    |    |     |     |    |         | 0x01 |    |    |         |    |    |    |        |      | 0x00  | GRID0 |

| GRID1 |    |    |    |    |     |     |    |         | 0x03 |    |    |         |    |    |    |        |      | 0x02  | GRID1 |

| GRID2 |    |    |    |    |     |     |    |         | 0x05 |    |    |         |    |    |    |        |      | 0x04  | GRID2 |

| GRID3 |    |    |    |    |     |     |    |         | 0x07 |    |    |         |    |    |    |        |      | 0x06  | GRID3 |

|       |    |    | -  |    |     |     |    |         |      |    |    |         |    |    |    | -      |      |       |       |

| GRID7 |    |    |    |    |     |     |    |         | 0x0F |    |    |         |    |    |    |        |      | 0x0E  | GRID7 |

|       | D7 | D6 | D5 | D4 | D3  | D2  | D1 | D0      |      | D7 | D6 | D5      | D4 | D3 | D2 | D1     | D0   |       |       |

Note:

At the initial system power on, the value stored in the chip display RAM may be random. It is recommended to clear the display RAM after power on, write 0x00 to the all display RAM (0x00-0x0f).

SEG pins connect to LED Anode, GRID pins connect to LED Cathode, Reverse connection is not allowed.

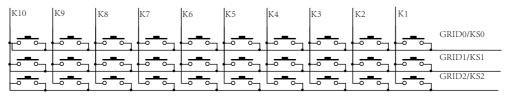

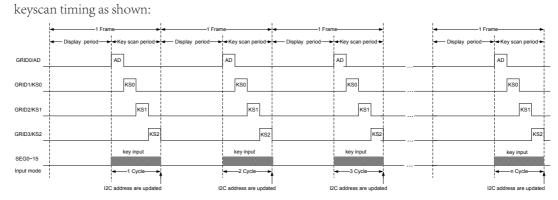

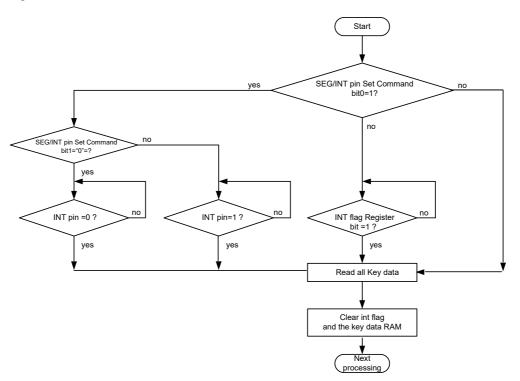

#### 3.5 Keyscan

#### 3.5.1 Key data reading

The key scanning is automatically completed by the hardware, only needs to read the key value through I2C. When a key is pressed, INT interrupt is generated. This interrupt flag can be read through I2C or output throughINT pin (open drain output). The keyscan cycle loops continuously over time, with all 30 keys(10x3) experiencing a full keyscanning debounce over 20ms. A key press is debounced and an interrupt issued if at least one key that was not pressed in a previous cycle is found to be pressed during both sampling periods. The keyscan circuit detects any combination of keys pressed during each debounce cycle (n-key rollover).

When after all the key data has been read that clears the key data RAM and the int flag bit is set to  $0^{\circ}$ , If the SEG / intINT pin is set to INT output, the INT pin returns to the level when no key is pressed.

INT flag Register:

| INT                 |             |             | Function    |             |             |             |             |             |                                                                |

|---------------------|-------------|-------------|-------------|-------------|-------------|-------------|-------------|-------------|----------------------------------------------------------------|

| Register<br>address | bit7        | bit6        | bit5        | bit4        | bit3        | bit2        | bit1        | bit0        | key press flag                                                 |

| 0x60                | INT<br>flag | bit7-bit0 set 1when<br>key press,when all<br>key read clear 0. |

The following shows the mapping from the RAM to the key data output:

| key         | 7      |        |        |        |        |        |         |        |  |  |

|-------------|--------|--------|--------|--------|--------|--------|---------|--------|--|--|

| RAM<br>addr | bit7   | bit6   | bit5   | bit4   | bit3   | bit2   | bit1    | bit0   |  |  |

| 0x40        | KS0/K8 | KS0/K7 | KS0/K6 | KS0/K5 | KS0/K4 | KS0/K3 | KS0/K2  | KS0/K1 |  |  |

| 0x41        | 0      | 0      | 0      | 0      | 0      | 0      | KS0/K10 | KS0/K9 |  |  |

| 0x42        | KS1/K8 | KS1/K7 | KS1/K6 | KS1/K5 | KS1/K4 | KS1/K3 | KS1/K2  | KS1/K1 |  |  |

| 0x43        | 0      | 0      | 0      | 0      | 0      | 0      | KS1/K10 | KS1/K9 |  |  |

| 0x44        | KS2/K8 | KS2/K7 | KS2/K6 | KS2/K5 | KS2/K4 | KS2K3  | KS2/K2  | KS2/K1 |  |  |

| 0x45        | 0      | 0      | 0      | 0      | 0      | 0      | KS2/K10 | KS2/K9 |  |  |

Note: It is recommended that the key data RAM is read only and should be started form address 0x40 only, the key data RAM of address 0X40~0X45 should be read continuously and in one operation.

## 3.5.2 Keyscan Timing

Note: The Slave addresses are updated on the keyscan timing

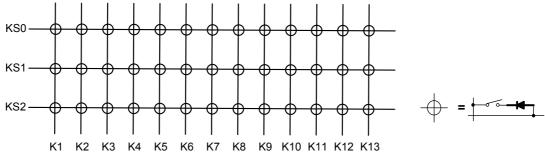

#### 3.5.3 Key Combination

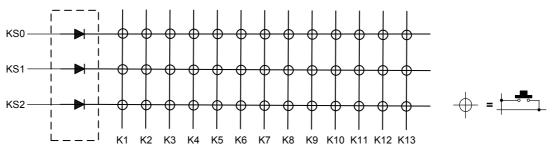

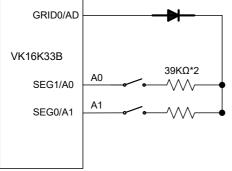

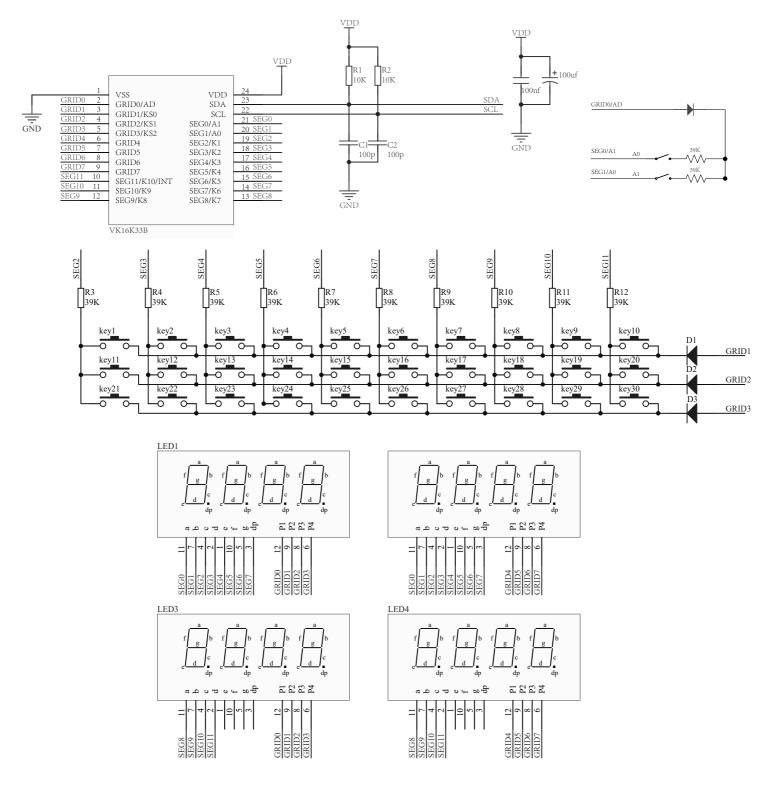

When pressing three or more times is assumed, each combination key is required to connect diodes in series, shown as below :

When pressing twice is assumed,KS0-KS2 is required to connect diodes in series, shown as below:

Note: In this circuit, pressing three or more times may cause the OFF switches to be determined as being ON.

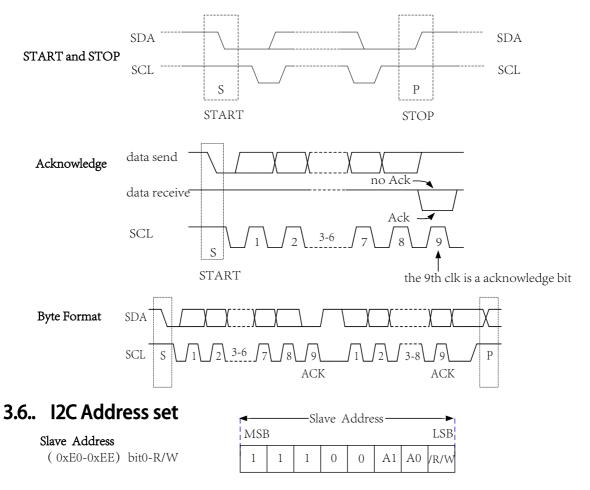

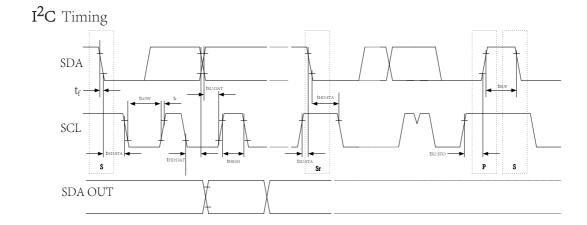

# 3.6 Communication Command3.6.1 I2C Serial Interface

The device supports I2C serial interface.

The two lines are a serial data line, SDA, and a serial clock line, SCL. Both lines are connected to the positive supply via pull-up resistors with a typical value of 4.7k. When the bus is free, both lines are high.

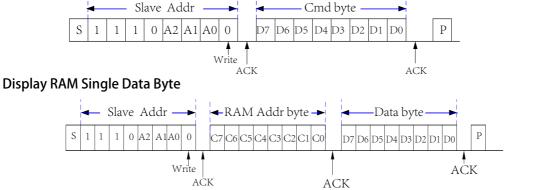

I2C slave address is selected through A2-A0 pins, and I2C slave address is updated during power <u>on reset or key s</u>canning cycle, shown as below :

Note: A1-A0 float is 0, connect is 1, when all float the device address is 0xE0

# 3.6.3 I2C Command Format

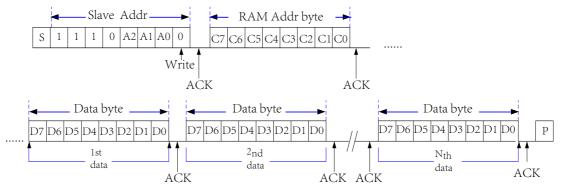

#### 3.6.3.1 Write Operation

#### Write Command

**Display RAM Page Write Operation**

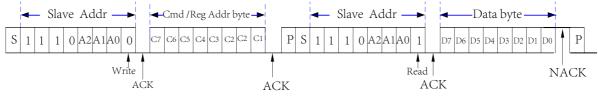

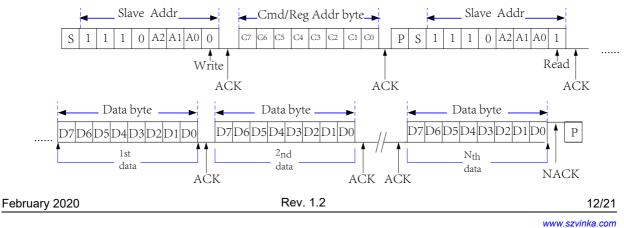

#### 3.6.2.2 Read Operation

Reading a data byte is not applicable to reading the key value.

Read n bytes data. The address pointer will auto-increase after received ACK. When reading the key, read 6 data continuously from start address 0x40.

# 3.6.6 Command Summary

#### 3.6.4.1 System Set Command

This command is used to set the work mode: Normal mode or Standby mode.

|   | bit7 | bit6 | bit5 | bit4 | bit3 | bit2 | bit1 | bit0 | Function          | Note                  | Def  |

|---|------|------|------|------|------|------|------|------|-------------------|-----------------------|------|

| ſ | 0    | 0    | 1    | 0    | V    | V    | V    | 0    | system oscillator | Standby mode(OSC off) | 0x20 |

|   | 0    | 0    | 1    | 0    | Х    | Λ    | Λ    | 1    | ON/OFF            | Normal mode(OSC on)   | 0720 |

#### 3.6.4.2 Display Set Command

This command is used to set the LED Display on/off and Blink Frequency.

| bit7 | bit6 | bit5 | bit4 | bit3 | bit2 | bit1 | bit0 | Function  | Note      | Def   |

|------|------|------|------|------|------|------|------|-----------|-----------|-------|

| 1    | 0    | 0    | 0    | Х    |      |      | 0    | Display   | Off       | 0x80  |

| 1    | 0    | 0    | 0    |      |      |      | 1    | On/Off    | On        | 0,000 |

| 1    | 0    | 0    | 0    |      | 0    | 0    |      |           | blink off |       |

| 1    | 0    | 0    | 0    |      | 0    | 1    |      | Blink     | 2Hz       | 0x80  |

| 1    | 0    | 0    | 0    | Х    | 1    | 0    |      | Frequency | 1Hz       | 0,000 |

| 1    | 0    | 0    | 0    |      | 1    | 1    |      |           | 0.5Hz     |       |

## 3.6.4.3 SEG/INT pin Set Command

This command is used to set the INT / SEG pin output function.

| bit7 | bit6 | bit5 | bit4 | bit3 | bit2 | bit1 | bit0 | Function                       | Note                 | Def     |

|------|------|------|------|------|------|------|------|--------------------------------|----------------------|---------|

| 1    | 0    | 1    | 0    |      |      | 0    | 0    | INT/SEG pin                    | SEG pin              | 077 4 0 |

| 1    | 0    | 1    | 0    | Х    | Х    | 0    | 1    | function select<br>and INT pin | INT pin,active low.  | 0xA0    |

| 1    | 0    | 1    | 0    |      |      | 1    | 1    | out level                      | INT pin,active high. |         |

**VK16K33B**

12×8 LED DRIVER

#### 3.6.4.3 Display Address Set Command

Set the address of the Display RAM (0x00 - 0x0f). When powered on, the address is set to 0x00(default).

| bit7 | bit6 | bit5 | bit4 | bit3 | bit2 | bit1 | bit0 | DisplayRAM Addr |

|------|------|------|------|------|------|------|------|-----------------|

| 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0x00            |

| 0    | 0    | 0    | 0    | 0    | 0    | 0    | 1    | 0x01            |

| 0    | 0    | 0    | 0    | 0    | 0    | 1    | 0    | 0x02            |

| 0    | 0    | 0    | 0    | 0    | 0    | 1    | 1    | 0x03            |

| 0    | 0    | 0    | 0    | 0    | 1    | 0    | 0    | 0x04            |

| 0    | 0    | 0    | 0    | 0    | 1    | 0    | 1    | 0x05            |

| 0    | 0    | 0    | 0    | 0    | 1    | 1    | 0    | 0x06            |

| 0    | 0    | 0    | 0    | 0    | 1    | 1    | 1    | 0x07            |

| 0    | 0    | 0    | 0    | 1    | 0    | 0    | 0    | 0x08            |

| 0    | 0    | 0    | 0    | 1    | 0    | 0    | 1    | 0x09            |

| 0    | 0    | 0    | 0    | 1    | 0    | 1    | 0    | 0x0A            |

| 0    | 0    | 0    | 0    | 1    | 0    | 1    | 1    | 0x0B            |

| 0    | 0    | 0    | 0    | 1    | 1    | 0    | 0    | 0x0C            |

| 0    | 0    | 0    | 0    | 1    | 1    | 0    | 1    | 0x0D            |

| 0    | 0    | 0    | 0    | 1    | 1    | 0    | 1    | 0x0E            |

| 0    | 0    | 0    | 0    | 1    | 1    | 1    | 1    | 0x0F            |

# 3.6.4.5 Display brightness Set Command

Set the Display brightness (level 16).

| bit7 | bit6 | bit5 | bit4 | bit3 | bit2 | bit1 | bit0 | Function        | Note       |

|------|------|------|------|------|------|------|------|-----------------|------------|

| 1    | 1    | 1    | 0    | 0    | 0    | 0    | 0    |                 | 1/16 duty  |

| 1    | 1    | 1    | 0    | 0    | 0    | 0    | 1    |                 | 2/16 duty  |

| 1    | 1    | 1    | 0    | 0    | 0    | 1    | 0    |                 | 3/16 duty  |

| 1    | 1    | 1    | 0    | 0    | 0    | 1    | 1    |                 | 4/16 duty  |

| 1    | 1    | 1    | 0    | 0    | 1    | 0    | 0    |                 | 5/16 duty  |

| 1    | 1    | 1    | 0    | 0    | 1    | 0    | 1    |                 | 6/16 duty  |

| 1    | 1    | 1    | 0    | 0    | 1    | 1    | 0    | Set <b>GRID</b> | 7/16 duty  |

| 1    | 1    | 1    | 0    | 0    | 1    | 1    | 1    | Pulse Width     | 8/16 duty  |

| 1    | 1    | 1    | 0    | 1    | 0    | 0    | 0    |                 | 9/16 duty  |

| 1    | 1    | 1    | 0    | 1    | 0    | 0    | 1    |                 | 10/16 duty |

| 1    | 1    | 1    | 0    | 1    | 0    | 1    | 0    |                 | 11/16 duty |

| 1    | 1    | 1    | 0    | 1    | 0    | 1    | 1    |                 | 12/16 duty |

| 1    | 1    | 1    | 0    | 1    | 1    | 0    | 0    |                 | 13/16 duty |

| 1    | 1    | 1    | 0    | 1    | 1    | 0    | 1    |                 | 14/16 duty |

| 1    | 1    | 1    | 0    | 1    | 1    | 1    | 0    |                 | 15/16 duty |

| 1    | 1    | 1    | 0    | 1    | 1    | 1    | 1    |                 | 16/16 duty |

February 2020

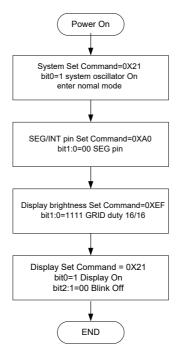

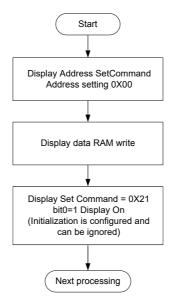

# 3.7 Command application

#### 3.7.1 Initialize configuration

During power on, the power on reset sequence shall be met. After power on, the parameters shall be configured first.

Config parameters through a series of commands. The command sequence is as follows:

#### 3.7.2 Display data Read Command

## 3.7.3 Key Read Command

It is recommended that the key data RAM is read only and should be started form address 0X40 only, the key data RAM of address 0X40~0X45 should be read continuously and in one operation.

# **4** Application Circuits

# **5** Electrical characteristics

### 5.1 Absolute Maximum Ratings

| Item                  | Symbol           | Ratings             | Unit |

|-----------------------|------------------|---------------------|------|

| Power voltage         | VDD              | VSS-0.3V to VSS+6.5 | V    |

| Input Voltage         | VIN              | VSS-0.3V to VDD+0.3 | V    |

| Storage Temperature   | Tstg             | -50~+120            | °C   |

| Operating Temperature | T <sub>OTG</sub> | -40~+85             | °C   |

# 5.2 DC Characteristics

| Symbol              | Item                                   | Min.                         | Тур. | Max.                | Unit |     | Test Conditions                                             |

|---------------------|----------------------------------------|------------------------------|------|---------------------|------|-----|-------------------------------------------------------------|

|                     |                                        |                              |      |                     |      | VDD | Conditions                                                  |

| V <sub>DD</sub>     | Operating voltage                      | 3.0                          | 5    | 5.5                 | V    | -   | -                                                           |

| I <sub>DD</sub>     | Operating current                      | -                            | 1    | 2                   | mA   | 5   | No load, normal mode<br>SEG/INT pin set 0                   |

| I <sub>STB</sub>    | Standby Current                        | -                            | 1    | 10                  | μΑ   | 5   | No load, standby mode                                       |

| V <sub>IH</sub>     | Input High Voltage                     | $0.7 \mathrm{V}_\mathrm{DD}$ | -    | V <sub>DD</sub>     | V    | 5   | SDA,SCL                                                     |

| V <sub>IL</sub>     | Input Low Voltage                      | 0                            | -    | $0.3 V_{\text{DD}}$ | V    | 5   | SDA,SCL                                                     |

| $I_{IL}$            | Input leakage current                  | -1                           | -    | μlA                 |      | -   | $V_{IN} = V_{SS}$ 或 $V_{DD}$                                |

| R <sub>PL</sub>     | Input pull-down<br>resistor            | 250                          |      | _                   | KΩ   | 5   | SEG3/K1~SEG15/K13,<br>SEG0/A2~SEG2/A0<br>Key scan period    |

| I <sub>OL1</sub>    | Low level output current               | 6                            | -    | -                   | mA   | 5   | V <sub>OL</sub> =0.4V; SDA                                  |

| I <sub>OL2</sub>    | SEG Sink Current                       | 6                            | -    | -                   | mA   | 5   | V <sub>OL</sub> =0.4V,INT pin                               |

| I <sub>OH1</sub>    | SEG Source Current                     | -20                          | -25  | -40                 | mA   | 5   | V <sub>OH</sub> =V <sub>DD</sub> -2V,(SEG0~SEG15)           |

| TOHI                | SEG Source Current                     | -25                          | -30  | -50                 | mA   |     | V <sub>OH</sub> =V <sub>DD</sub> -3V,(SEG0~SEG15)           |

| I <sub>TOLSEG</sub> | High level output<br>current tolerance | -                            | -    | 5                   | %    | 5   | V <sub>OH</sub> =V <sub>DD</sub> -3V,(SEG0~SEG15)           |

| I <sub>OL3</sub>    | GRID Sink Current                      | 160                          | 200  | -                   | mA   | 5   | V <sub>OL</sub> =0.3V,(GRID0~GRID7 pin)                     |

| I <sub>OH2</sub>    | GRID Source Current                    | -20                          | -25  | -40                 | mA   | 5   | V <sub>OH</sub> = V <sub>DD</sub> -2V,<br>(GRID0~GRID3 pin) |

# VK16K33B 12×8 LED DRIVER

# 5.3 AC Characteristics

| Same h al            | Item                                            | Min.    | Max.   | Unit | Test Conditions                                                        |

|----------------------|-------------------------------------------------|---------|--------|------|------------------------------------------------------------------------|

| Symbol               | item                                            | Iviiii. | Iviax. |      | Conditions                                                             |

| $f_{\rm SCL}$        | Clock Frequency                                 | -       | 400    | kHZ  | —                                                                      |

| t <sub>BUF</sub>     | Bus Free Time                                   | 1.3     | -      | μs   | Time in which the bus must be free before a new transmission can start |

| t <sub>hd; sta</sub> | Start Condition<br>Hold Time                    | 0.6     | -      | μs   | After this period,<br>the first clock pulse is generated               |

| t <sub>LOW</sub>     | SCL Low Time                                    | 1.3     | -      | μs   | —                                                                      |

| t <sub>HIGH</sub>    | SCL High Time                                   | 0.6     | -      | μs   | —                                                                      |

| t <sub>su; sta</sub> | Start Condition<br>Setup Time                   | 0.6     | -      | μs   | Only relevant for repeated<br>START condition                          |

| t <sub>hd; dat</sub> | Data Hold Time                                  | 0       | -      | μs   | —                                                                      |

| t <sub>su; dat</sub> | Data Setup Time                                 | 100     | -      | ns   | —                                                                      |

| t <sub>r</sub>       | Rising Time                                     | -       | 0.3    | μs   | periodically sampled                                                   |

| t <sub>f</sub>       | Falling Time                                    | -       | 0.3    | μs   | periodically sampled                                                   |

| t <sub>su; sto</sub> | Stop Condition<br>Setup Time                    | 0.6     | -      | μs   | —                                                                      |

| tAA                  | Output Valid<br>from Clock                      | -       | 0.9    | μs   | _                                                                      |

| t <sub>SP</sub>      | Input Filter Time Constant<br>(SDA and SCL pin) | -       | 50     | ns   | Noise suppression time                                                 |

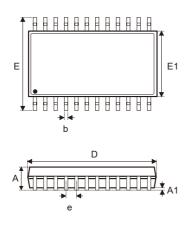

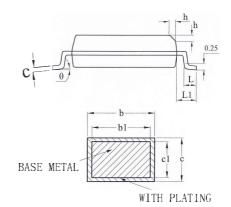

# 6 Package Information

# 6.1 SOP24 (300mil) (15.40mm x 7.5mm PP=1.27mm)

| SYMBOL  | MILLIMETER |       |       |  |

|---------|------------|-------|-------|--|

| STNIDOL | MIN        | NOM   | MAX   |  |

| A       |            |       | 2.64  |  |

| A1      | 0.10       | 0.20  | 0.30  |  |

| b       | 0.39       |       | 0.47  |  |

| b1      | 0.38       | 0.41  | 0.44  |  |

| с       | 0.25       |       | 0.29  |  |

| c1      | 0.24       | 0.25  | 0.26  |  |

| D       | 15.30      | 15.40 | 15.50 |  |

| E       | 10.10      | 10.30 | 10.50 |  |

| E1      | 7.40       | 7.50  | 7.60  |  |

| e       | 1.27BSC    |       |       |  |

| h       | 0.25       |       | 0.75  |  |

| L       | 0.70       |       | 1.00  |  |

| L1      | 1.40REF    |       |       |  |

# 7 Revision history

| No. | Version | Date       | Modify the content | Check |

|-----|---------|------------|--------------------|-------|

| 1   | 1.0     | 2018-08-10 | Original version   | Yes   |

| 2   | 1.1     | 2019-07-11 | Add Ref circuits   | Yes   |

| 3   | 1.2     | 2020-02-11 | Update content     | Yes   |

|     |         |            |                    |       |

#### Disclaimers

Information in this document is believed to be accurate and reliable. However, VinKa does not give any representations or warranties, expressed or implied, as to the accuracy or completeness of such information. VinKa reserves the right to make changes to information published in this document, including without limitation specifications and product descriptions, at any time and without notice. This document supersedes and replaces all information supplied prior to the publication hereof. For the latest information, please visit https://www.szvinka.com Or contact VinKa's staff.